Copyright © 2006 by Jaidev Prasad Patwardhan All rights reserved

#### ARCHITECTURES FOR NANOSCALE DEVICES

by

Jaidev Patwardhan

Department of Computer Science Duke University

Date: \_\_\_\_\_

Approved:

Professor Alvin R. Lebeck, Advisor

Professor Christopher Dwyer

Professor John Reif

Professor Eric Rotenberg

Professor Daniel J. Sorin

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University

2006

#### ABSTRACT

#### ARCHITECTURES FOR NANOSCALE DEVICES

by

Jaidev Patwardhan

Department of Computer Science Duke University

Date: \_\_\_\_\_

Approved:

Professor Alvin R. Lebeck, Advisor

Professor Christopher Dwyer

Professor John Reif

Professor Eric Rotenberg

Professor Daniel J. Sorin

An abstract of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University

2006

## Abstract

The semiconductor industry's roadmap identifies a "red brick wall" beyond which it is unknown how to extend the historical trend of ever-decreasing CMOS device size. While architectural innovations can provide short-term relief, there is a need to explore long-term alternatives to CMOS devices and fabrication techniques. A revolutionary technology change, such as replacing CMOS, is a potentially disruptive event in the design of computing systems. Emerging technologies for further miniaturization have capabilities and limitations that can significantly influence computer architecture and require re-examining or rebuilding abstractions originally tailored for CMOS.

DNA-based self-assembly of nanoscale components is a promising alternative to CMOS that holds the potential to usher in an era of tera- to peta-scale integration. Although much of this technology is in its infancy, by studying its potential uses for building computing systems, architects can better understand its opportunities and limitations while providing feedback to scientists developing the technologies. This thesis explores the architectural challenges introduced by bottom-up fabrication of nanoelectronic circuits. The goal is to design high-performance defect-tolerant architectures within technological constraints. While our designs assume one specific technology, they are compatible with other technologies with similar characteristics.

We make four primary contributions in this thesis. First, we propose a circuit architecture that enables the construction of circuits that balance three conflicting goals: 1) regularity for the DNA lattice, 2) complexity for the circuit, and 3) defect tolerance. This enables the creation of a large number of circuit elements (nodes) with basic compute and communication capabilities, connected in a random network. Second, we adapt an existing algorithm to isolate defective nodes and provide logical structure to the random network. Third, we design a general purpose architecture (Nanoscale Active Network Architecture or NANA) that exploits this logical structure to create execution and memory networks that can execute programs. Fourth, we design a data parallel architecture (Self-Organizing SIMD Architecture or SOSA) that exploits hardware parallelism in the network to create a high-performance defect tolerant architecture. SOSA achieves the primary goal of this thesis by attaining performance equivalent to modern processors, while operating at a lower speed and consuming lesser power.

### Acknowledgments

Throughout this Ph.D. thesis, I have benefited from the support, encouragement and guidance of family, mentors, colleagues and friends. This is where I get to express my gratitude towards them.

My wife, Lavanya, has been my pillar of strength through my time in graduate school. She has helped me in innumerable ways, from providing feedback on writing and presentations, to providing a sounding board for my ideas. I hope I can provide the same level of support to her in the future.

I am thankful to both our families for supporting us through these six years. I would especially like to thank my parents who instilled in me a sense of curiosity and wonder at a very young age, and they deserve much credit for my accomplishments. My sister and brother-in-law helped make my transition from life in India to the U.S as smooth as possible.

I could not have asked for a better advisor than Alvin Lebeck. Alvy has been an excellent mentor and guide, and has been instrumental in my development as a researcher. He always seemed to know how to motivate me to do better and struck the right balance between independence and supervision.

I have also been very fortunate to have gotten to work closely with Daniel Sorin and Chris Dwyer through my thesis work. Their ideas, insights and guidance have helped me become a better researcher. I would also like to thank Eric Rotenberg and John Reif for taking the time to serve on my committee and provide feedback.

Through graduate school, I have had the support of many friends and colleagues. I would like to thank all members of the Duke Computer Architecture group, past and present, for stimulating discussions, feedback and providing unique perspectives on problems. I would specifically like to thank three members of the group who were great role models and sources of support and guidance - Srikanth Srinivasan, Mithuna Thottethodi and Tong Li.

I am thankful for the great officemates and roommates I have had during my time at Duke - Omer Asad, David Irwin, Rahul Lakhotia, Parag Palekar, Constantin Pistol, Abhijit Vijay, Mithuna Thottethodi, and Kashi Vishwanath. They have been the source of some extremely stimulating conversations. I would also like to thank Andrew Danner and Laura Grit for some great discussions over lunch and coffee. I have been fortunate to have made other good friends at Duke, including Padmaja Ayyagari, Juhi Juneja, Suparna Kanjilal, Pramod Kolar, Vijay Natarajan, Vamsee Pamula, Shobana Ravi, Vinay Singh, and Vijay Srinivasan.

I am extremely grateful to Diane Riggs for making life as a graduate student in this department as smooth as possible. Diane is one of the most hard-working and helpful people I have ever met and I could not imagine what life would be like in the department without Diane's steady presence.

Last, but not least, I would like to thank my late grandfather, Upendra Patwardhan, for being a tremendous source of inspiration and for convincing me to attend Duke. This thesis is dedicated to his memory.

## **Table of Contents**

| Abstrac                          | etiv                                                                                                                                                               |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknov                           | vledgments                                                                                                                                                         |

| List of '                        | <b>Fables</b>                                                                                                                                                      |

| List of ]                        | Figures                                                                                                                                                            |

| CHAP                             | <b>FER 1</b> Introduction                                                                                                                                          |

| 1.2 I                            | Thesis Statement and Contributions       .3         mpact of DNA-based Self-Assembly of Nanoelectronic Components on       .4         Architecture Design       .4 |

|                                  | Defect Tolerance                                                                                                                                                   |

|                                  | mproving Network Connectivity                                                                                                                                      |

| CHAPT                            | <b>TER 2 DNA-Based Self-Assembly of Nanoelectronic Devices</b>                                                                                                     |

| 2.2 I<br>2.3 H                   | End of Silicon Based CMOS10DNA-based Self-Assembly11Emerging Nanoelectronic Devices13DNA-based Self-Assembly of Carbon Nanotube Electronics15                      |

| CHAPT                            | <b>FER 3 Implications for Architecture Design</b>                                                                                                                  |

| 3.1 I<br>3.1.1<br>3.1.2<br>3.1.3 | Complexity                                                                                                                                                         |

|                                  | Vanoelectronic Circuit Building Blocks                                                                                                                             |

| 3.2.1<br>3.2.2                   |                                                                                                                                                                    |

| 3.2.3                            | 8                                                                                                                                                                  |

| 3.2.4<br>3.2.5                   |                                                                                                                                                                    |

| 3.3 A                            | Architectural Implications                                                                                                                                         |

| 3.3.1<br>3.3.2                   | Small-scale Control.28Large-Scale Randomness.29                                                                                                                    |

| 3.3.3 High Defect Rates                                                                   |                           |

|-------------------------------------------------------------------------------------------|---------------------------|

| 3.4 Architectural Challenges                                                              |                           |

| 3.5 Summary                                                                               |                           |

| CHAPTER 4 Logical Structure and Defect Iso                                                | lation in Dandom Natworks |

| of Nodes                                                                                  |                           |

|                                                                                           |                           |

| 4.1 Node Functionality and Defect Model                                                   |                           |

| 4.2 Reverse Path Forwarding                                                               |                           |

| 4.3 Evaluation                                                                            |                           |

| 4.3.1 Experimental Setup                                                                  |                           |

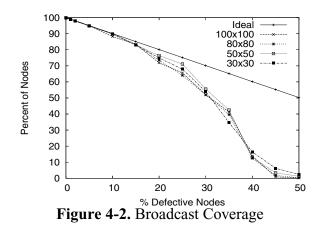

| 4.3.2 Broadcast Coverage                                                                  |                           |

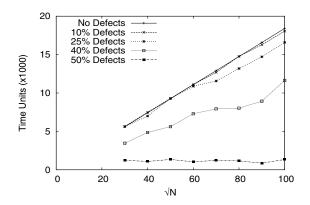

| 4.3.3 Broadcast Latency                                                                   |                           |

| <ul><li>4.3.4 Changing Broadcast Source</li><li>4.3.5 Broadcast Tree Properties</li></ul> |                           |

|                                                                                           |                           |

| <ul><li>4.4 Extending Gradient Broadcast</li><li>4.5 Conclusion</li></ul>                 |                           |

| 4.5 Conclusion                                                                            |                           |

| CHAPTER 5 Nano-Scale Active Network Arch                                                  | <b>nitecture</b>          |

| 5.1 NANA Overview                                                                         |                           |

| 5.2 Execution Model and Instruction Set                                                   |                           |

| 5.2.1 Execution Model                                                                     |                           |

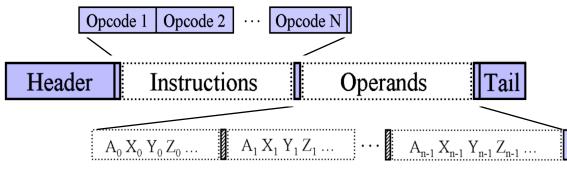

| 5.2.2 Execution Packet                                                                    |                           |

| 5.2.3 Instruction Set                                                                     |                           |

| 5.2.4 Configuration and Routing                                                           |                           |

| 5.2.4.1 Routing Execution Packets                                                         |                           |

| 5.2.4.2 Improving Node Utilization                                                        |                           |

| 5.3 Memory System                                                                         |                           |

| 5.3.1 Memory Allocation                                                                   |                           |

| 5.3.2 Interfacing Execution and Memory                                                    |                           |

| 5.3.3 Routing Memory Packets                                                              |                           |

| 5.4 Node Architecture                                                                     |                           |

| 5.4.1 Common Functionality                                                                |                           |

| 5.4.2 Processing/ALU Node                                                                 |                           |

| 5.4.3 Memory Node                                                                         |                           |

| 5.4.4 Memory Port Node                                                                    |                           |

| 5.5 Executing Programs                                                                    |                           |

| 5.6 Evaluation                                                                            |                           |

| 5.6.1 Evaluation Framework                                                                |                           |

| 5.6.2 Peak Performance                                                                    |                           |

| 5.6.3  | Estimating Instruction Execution Time                 | 67  |

|--------|-------------------------------------------------------|-----|

| 5.6.4  | Fibonacci                                             | 69  |

| 5.6.5  | String Match.                                         | 71  |

| 5.6.6  | Memory System: Queuing Network Model                  | 71  |

| 5.6.7  | Effect of System Optimizations                        | 75  |

| 5.6.7  | 7.1 Routing in the Execution Network                  | 75  |

| 5.6.7  | 7.2 Memory System Optimizations                       | 76  |

| 5.7 Pe | erformance Discussion                                 | 76  |

| 5.7.1  | Under-utilization of Nodes                            | 76  |

| 5.7.2  | Memory System Bottleneck                              | 77  |

| 5.8 In | sights and Lessons                                    | 77  |

| 5.8.1  | Configuration, Logical Structure and Defect Isolation | 78  |

| 5.8.2  | Heterogeneous Nodes                                   | 78  |

| 5.8.3  | Bit-level parallelism                                 | 78  |

| 5.8.4  | Exploiting Node Parallelism                           | 78  |

| 5.9 Co | onclusions                                            | 79  |

| СНАРТІ | ER 6 A Self-Organizing SIMD Architecture              | 80  |

| CHAIII |                                                       |     |

| 6.1 Sy | ystem Overview                                        | 82  |

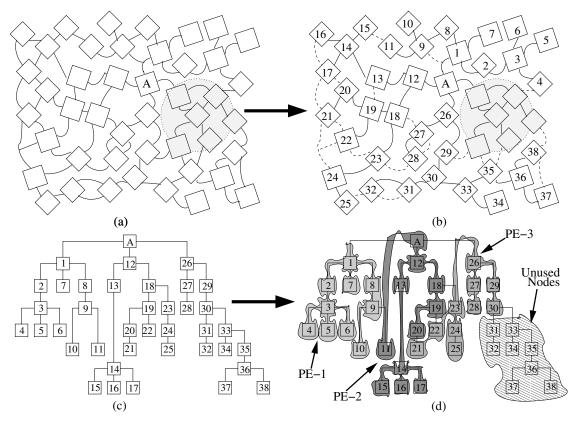

| 6.2 No | ode Microarchitecture                                 | 83  |

| 6.2.1  | Data Path                                             |     |

| 6.2.2  | Control                                               | 84  |

| 6.2.3  | Inter-Node Communication                              | 86  |

| 6.2.4  | Circuit Size and Power Estimates                      |     |

| 6.2.5  | Summary                                               |     |

| 6.3 Sy | ystem Configuration                                   | 88  |

| 6.3.1  | Configuring Processing Elements                       | 88  |

| 6.3.2  | Optimizing PE Configuration                           | 90  |

| 6.4 Sy | ystem Architecture                                    | 91  |

| 6.4.1  | Instruction Set Architecture                          | 91  |

| 6.4.2  | Execution Model                                       | 93  |

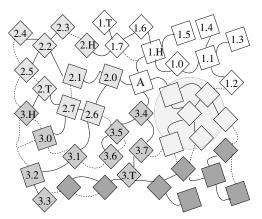

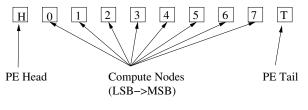

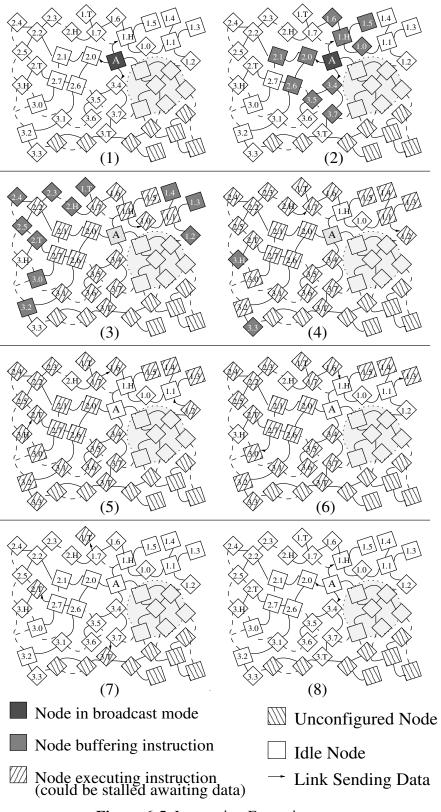

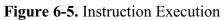

| 6.4.3  | Instruction Execution Example                         | 93  |

| 6.4.4  | Microinstruction Reuse                                | 95  |

| 6.4.5  | Summary                                               | 97  |

| 6.5 Ev | valuation                                             | 97  |

| 6.5.1  | Experimental Methodology                              | 98  |

| 6.5.1  | .1 Benchmarks                                         | 99  |

| 6.5.1  | .2 Extrapolation                                      | 100 |

| 6.5.2  | Peak Performance                                      | 101 |

| .102                                                                                         |

|----------------------------------------------------------------------------------------------|

| .103                                                                                         |

| .105                                                                                         |

| .108                                                                                         |

| .109                                                                                         |

| .109                                                                                         |

| .110                                                                                         |

| .111                                                                                         |

| .112                                                                                         |

| .113                                                                                         |

| .114                                                                                         |

| .114                                                                                         |

| .115                                                                                         |

| .116                                                                                         |

| .116                                                                                         |

| .119                                                                                         |

| .119                                                                                         |

| .120                                                                                         |

| .120                                                                                         |

| .122                                                                                         |

| .123                                                                                         |

|                                                                                              |

|                                                                                              |

| .124                                                                                         |

| .124<br>.124                                                                                 |

| .124<br>.124<br>.125                                                                         |

| .124<br>.124<br>.125<br>.127                                                                 |

| .124<br>.124<br>.125<br>.127<br>.128                                                         |

| .124<br>.124<br>.125<br>.127<br>.128<br>.129                                                 |

| .124<br>.124<br>.125<br>.127<br>.128<br>.129<br>.130                                         |

| .124<br>.125<br>.127<br>.128<br>.129<br>.130<br>.131                                         |

| .124<br>.125<br>.127<br>.128<br>.129<br>.130<br>.131<br>.132                                 |

| .124<br>.125<br>.127<br>.128<br>.129<br>.130<br>.131<br>.132<br>.132                         |

| .124<br>.125<br>.127<br>.128<br>.129<br>.130<br>.131<br>.132<br>.132<br>.134                 |

| .124<br>.125<br>.127<br>.128<br>.129<br>.130<br>.131<br>.132<br>.132<br>.134<br>.137         |

| .124<br>.125<br>.127<br>.128<br>.129<br>.130<br>.131<br>.132<br>.132<br>.132<br>.134<br>.137 |

| .124<br>.125<br>.127<br>.128<br>.129<br>.130<br>.131<br>.132<br>.132<br>.134<br>.137         |

| .124<br>.125<br>.127<br>.128<br>.129<br>.130<br>.131<br>.132<br>.132<br>.132<br>.134<br>.137 |

|                                                                                              |

| 8.3 Experimental Setup and Evaluation14          | 43 |

|--------------------------------------------------|----|

| 8.3.1 Topology Generator                         | 44 |

| 8.3.2 Modeling Infinite Backoff                  | 44 |

| 8.3.3 Modeling Links as Buses                    | 45 |

| 8.3.4 Methodology and Experiments                | 46 |

| 8.3.5 Network Connectivity                       | 46 |

| 8.3.6 Effect of Decaying Growth Rate             |    |

| 8.3.7 System Performance                         |    |

| 8.3.8 Effect of Defects                          |    |

| 8.4 Conclusions                                  | 53 |

| CHAPTER 9 Related Work                           | 54 |

| 9.1 CMOS-based Architectures                     | 54 |

| 9.2 Architectures based on Emerging Technologies | 55 |

| CHAPTER 10 Summary and Conclusions               | 59 |

| Appendix A: NANA Instruction Set                 | 52 |

| A.1 Arithmetic Instructions                      | 53 |

| A.2 Logical Instructions                         | 53 |

| A.3 Operand Stream Control Instructions16        | 55 |

| A.4 Comparison Instructions16                    | 57 |

| A.5 Memory Instructions16                        | 59 |

| A.5.1 Load Instructions                          | 59 |

| A.5.2 Store Instructions                         | 59 |

| A.5.3 Conditional Store Instructions             | 70 |

| A.5.4 Control Transfer Instructions              | 71 |

| Appendix B: SOSA Instruction Set                 | 74 |

| B.1 Arithmetic Instructions                      | 75 |

| B.2 Logical Instructions                         | 77 |

| B.3 Bit Shift Instructions                       | 78 |

| B.4 Predicate Modifying Instructions18           | 30 |

| B.5 Comparison Instructions18                    | 81 |

| B.6 Miscellaneous and Pseudo-Instructions18      | 82 |

| B.7 Programming SOSA - Matrix Multiplication     | 83 |

| Bibliography                                     | 36 |

| Biography                                        | 02 |

## **List of Tables**

| Table 4-1. | Properties of Broadcast Trees (100x100 network)42                  |

|------------|--------------------------------------------------------------------|

| Table 5-1. | NANA Instruction Set                                               |

| Table 5-2. | Definitions of a selected subset of instructions                   |

| Table 5-3. | Memory layout for two packets that compute $x=x+*(y+a)$ 53         |

| Table 5-4. | Packet Layout                                                      |

| Table 5-5. | Model Parameters                                                   |

| Table 6-1. | Instruction Set                                                    |

| Table 6-2. | SOSA System Parameters                                             |

| Table 6-3. | Ideal Superscalar Parameters                                       |

| Table 6-4. | Benchmark Descriptions100                                          |

| Table 6-5. | Peak Performance Comparison102                                     |

| Table 6-6. | TEA Throughput109                                                  |

| Table 6-7. | Search and bin packing throughput110                               |

| Table 7-1. | Node Component Classification                                      |

| Table 7-2. | Node Failure Modes                                                 |

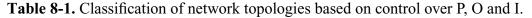

| Table 8-1. | Classification of network topologies142                            |

| Table 8-2. | Percentage of nodes reachable with varying device reliabilities152 |

| Table A-1. | NANA Instruction Set162                                            |

| Table B-1. | SOSA Instruction Set174                                            |

| Table B-2. | Instruction Bit Definitions                                        |

## **List of Figures**

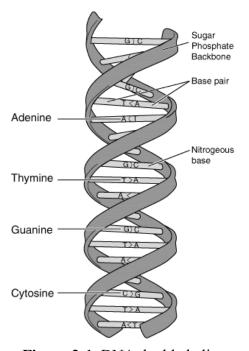

| Figure 2-1.  | DNA double helix                                                       |

|--------------|------------------------------------------------------------------------|

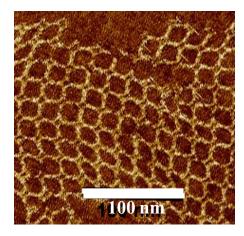

| Figure 2-2.  | DNA lattice with repeating cavities [105]12                            |

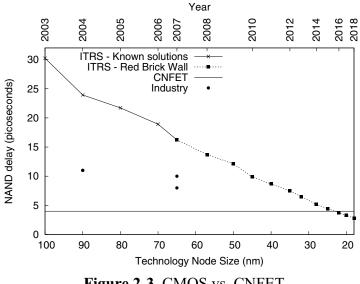

| Figure 2-3.  | CMOS vs. CNFET                                                         |

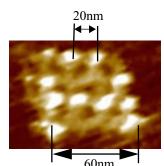

| Figure 2-4.  | A DNA scaffold for nano-electronic circuits with patterned letter A 15 |

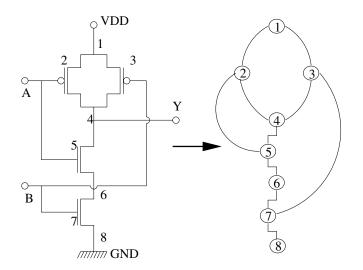

| Figure 3-1.  | Two input CMOS NAND gate, and equivalent graph20                       |

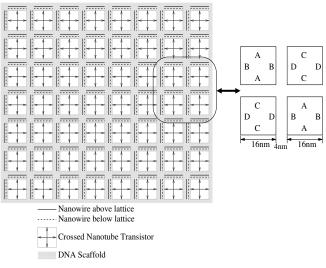

| Figure 3-2.  | DNA Scaffold for Nanoelectronics                                       |

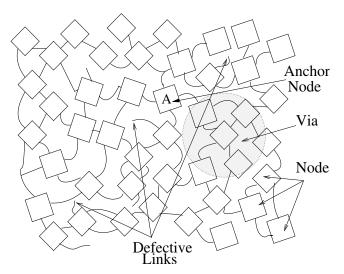

| Figure 3-3.  | Schematic of self-assembled network of nodes                           |

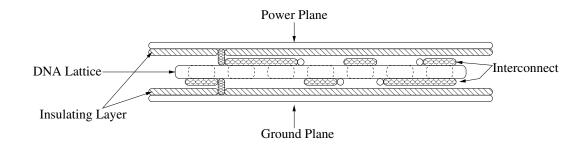

| Figure 3-4.  | External power and ground planes27                                     |

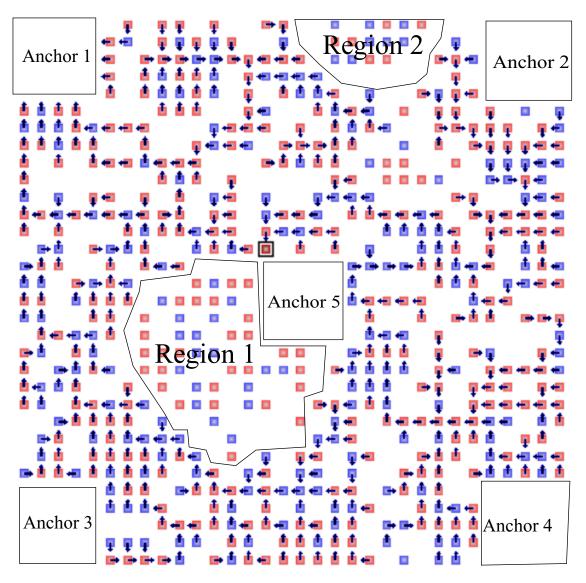

| Figure 4-1.  | Gradient directions in a small network of nodes                        |

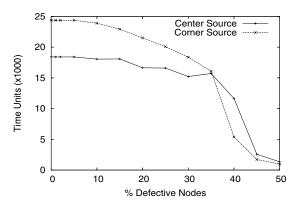

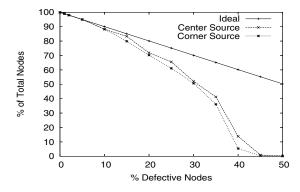

| Figure 4-2.  | Broadcast Coverage                                                     |

| Figure 4-3.  | Broadcast latency as a function of                                     |

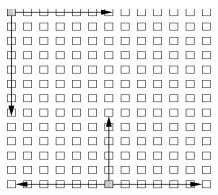

| Figure 4-4.  | Two possible options for gradient sources40                            |

| Figure 4-5.  | Broadcast latency as a function of the fraction of defective nodes41   |

| Figure 4-6.  | Varying Gradient Source:% Reachable Nodes41                            |

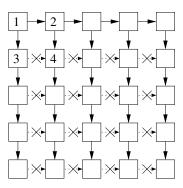

| Figure 4-7.  | Gradient Broadcast: Cause of low branching factor43                    |

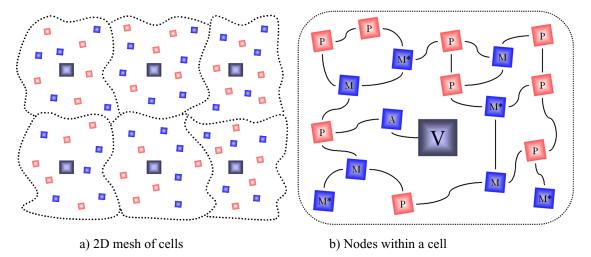

| Figure 5-1.  | System Model                                                           |

| Figure 5-2.  | Execution Packet Format                                                |

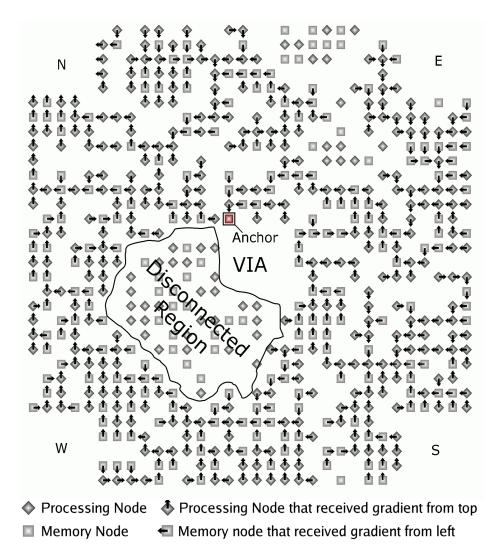

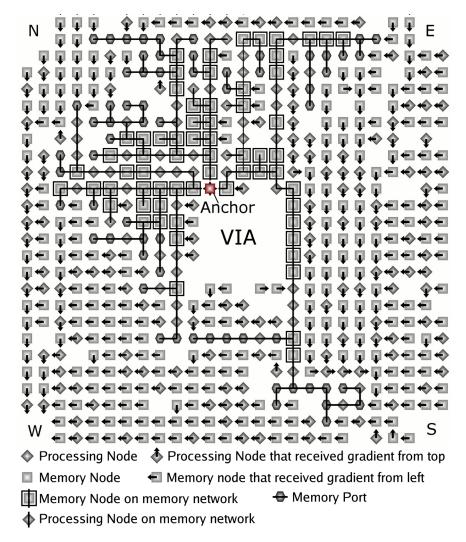

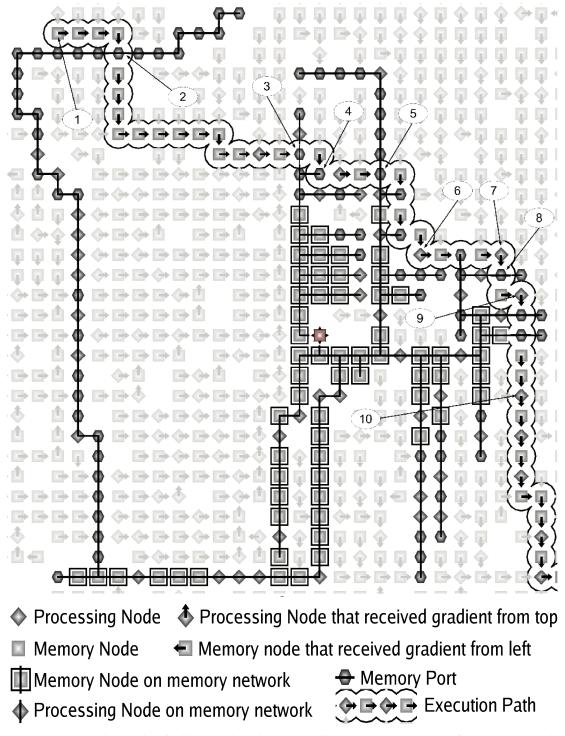

| Figure 5-3.  | A 32x32 grid of memory and processing nodes55                          |

| Figure 5-4.  | Memory Network                                                         |

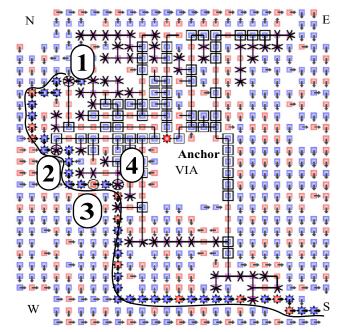

| Figure 5-5.  | The path of a simple code fragment65                                   |

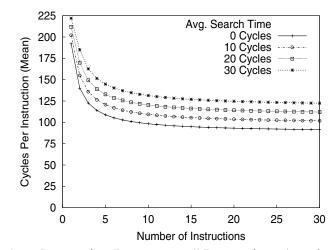

| Figure 5-6.  | Avg. Instruction Latency vs. # Instructions (varying search time)68    |

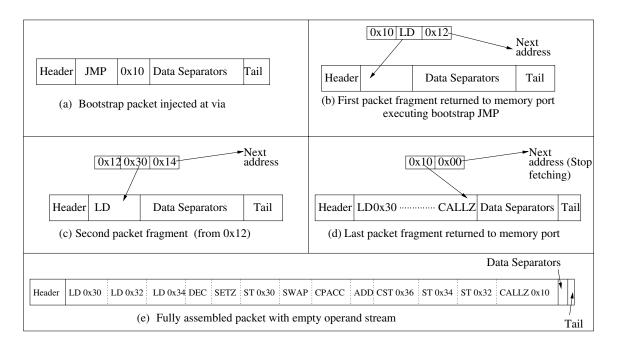

| Figure 5-7.  | Bootstrapping the fibonacci execution packet with a JMP70              |

| Figure 5-8.  | The path of Fibonacci code in one direction72                          |

| Figure 5-9.  | Memory Queuing Model73                                                 |

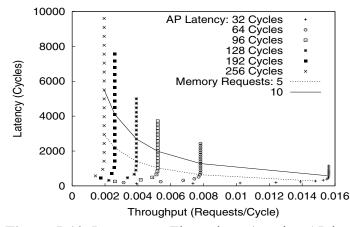

| Figure 5-10. | Latency vs. Throughput (varying AP latency)74                          |

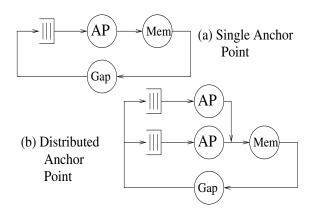

| Figure 5-11. | Multiple Anchor Points: Throughput vs. Latency75                       |

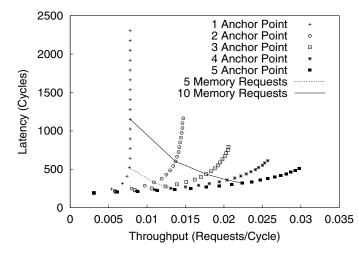

| Figure 6-1.  | Random Node Network                                                    |

| Figure 6-2.  | Node Floorplan                                                    |

|--------------|-------------------------------------------------------------------|

| Figure 6-3.  | System Overview                                                   |

| Figure 6-4.  | PE Layout90                                                       |

| Figure 6-5.  | Instruction Execution                                             |

| Figure 6-6.  | Reducing Broadcast Bandwidth: Micro-instruction reuse96           |

| Figure 6-7.  | Effective Instruction Latency101                                  |

| Figure 6-8.  | Matrix Multiply: Assembly Code (no unrolling)104                  |

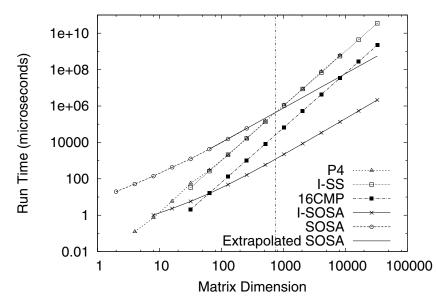

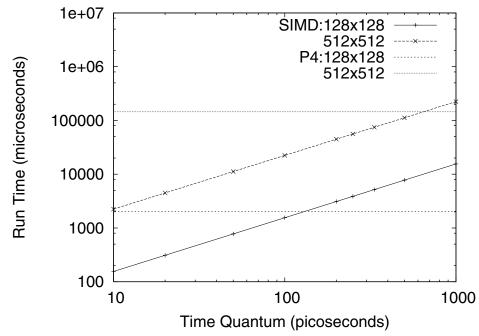

| Figure 6-9.  | Matrix Multiply Run Time105                                       |

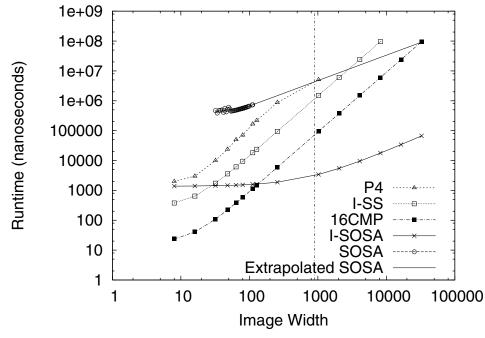

| Figure 6-10. | Gaussian Filter Runtime106                                        |

| Figure 6-11. | Generic Filter Runtime107                                         |

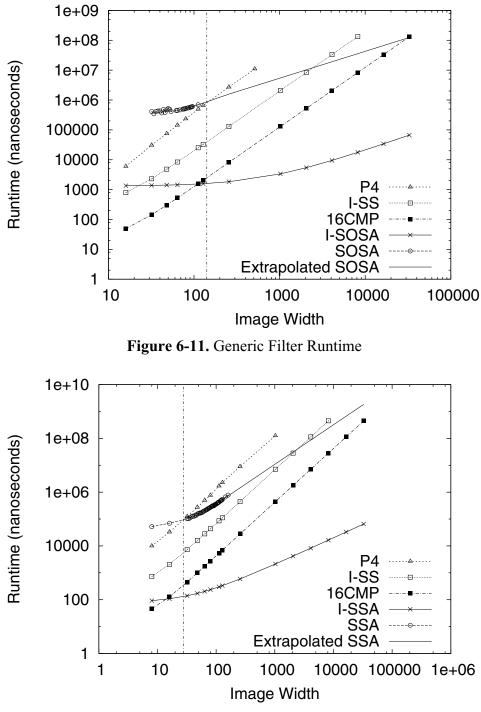

| Figure 6-12. | Median Filter Runtime107                                          |

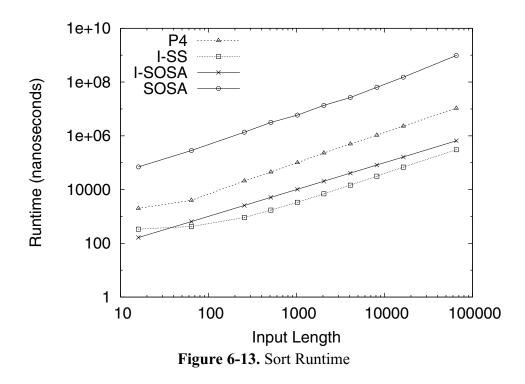

| Figure 6-13. | Sort Runtime                                                      |

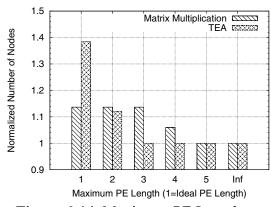

| Figure 6-14. | Maximum PE Length vs. Number of nodes111                          |

| Figure 6-15. | Maximum PE Length vs. running time111                             |

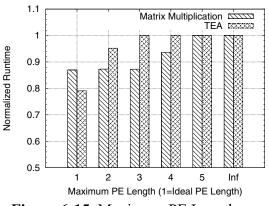

| Figure 6-16. | Effect of instruction reuse112                                    |

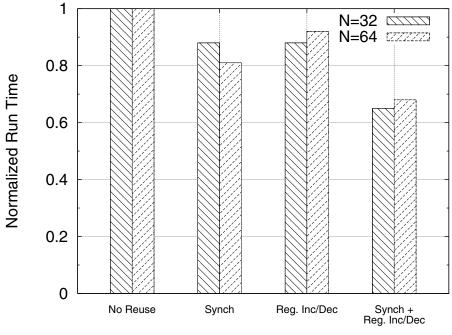

| Figure 6-17. | Sensitivity to Register Widths113                                 |

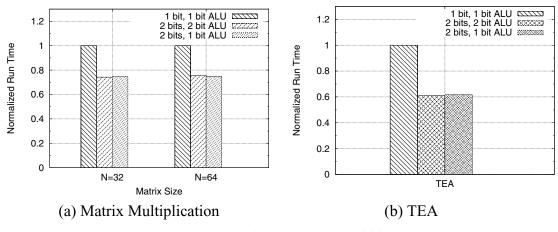

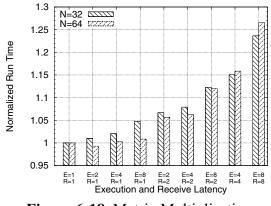

| Figure 6-18. | Matrix Multiplication: Varying execution and receive latency114   |

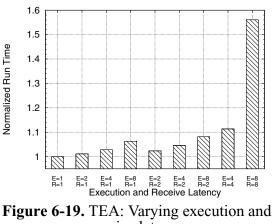

| Figure 6-19. | TEA: Varying execution and receive latency114                     |

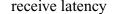

| Figure 6-20. | Performance sensitivity to instruction buffer size115             |

| Figure 6-21. | Running time of matrix multiply for different time unit values116 |

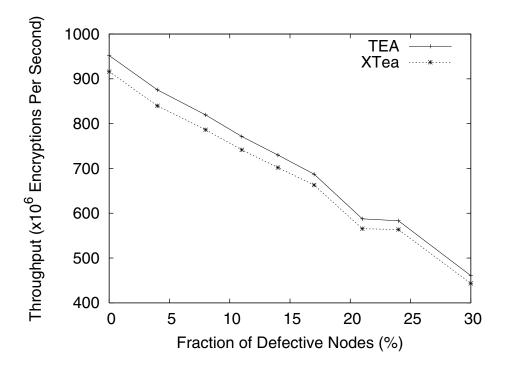

| Figure 6-22. | TEA/XTEA: Graceful degradation of throughput118                   |

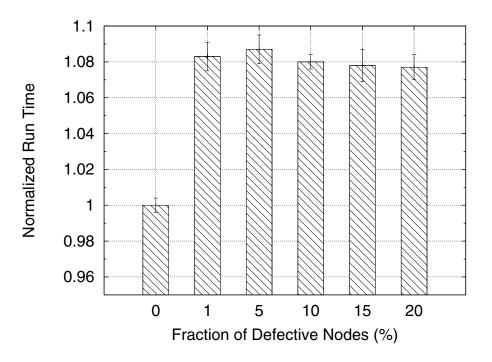

| Figure 6-23. | Matrix multiply performance with defects                          |

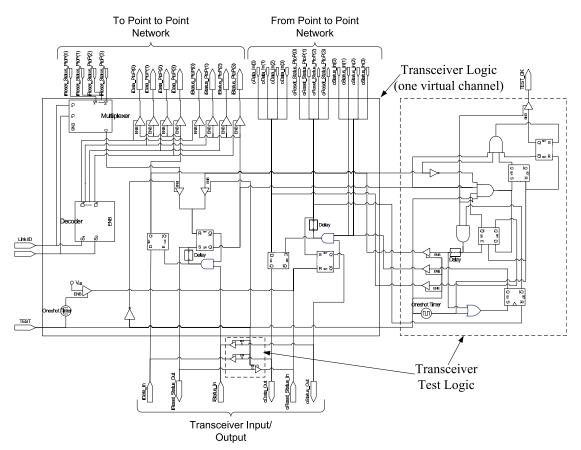

| Figure 7-1.  | Transceiver logic for one virtual channel                         |

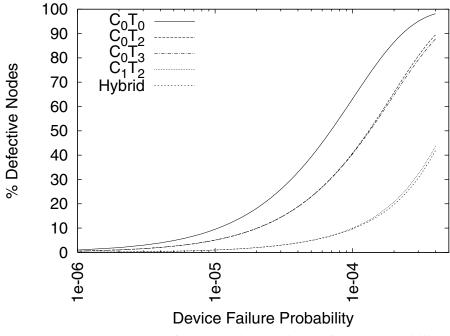

| Figure 7-2.  | Percentage defective nodes vs. device failure probability         |

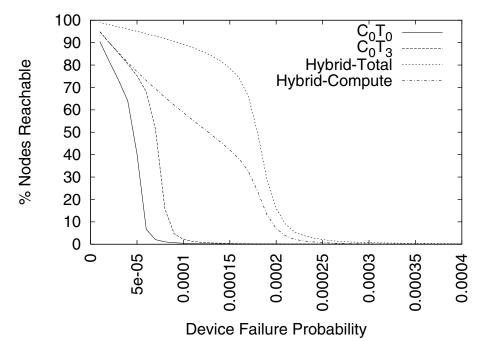

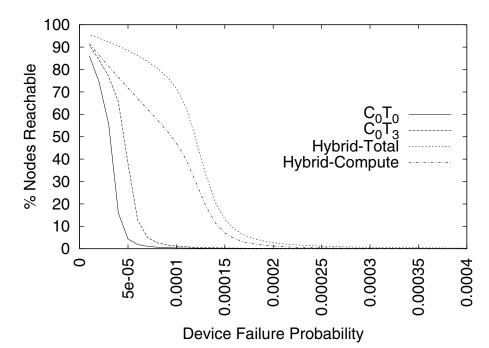

| Figure 7-3.  | Percentage Nodes Reachable vs. Device Failure Probability         |

| Figure 7-4.  | Percentage Reachable Nodes vs. Device Failure Probability         |

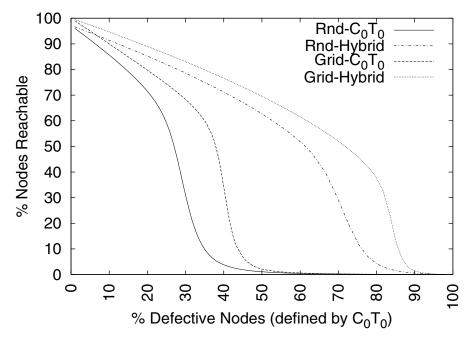

| Figure 7-5.  | Effect of using nodes with some defective components              |

| Figure 8-1.  | Examples of eight networks142                                     |

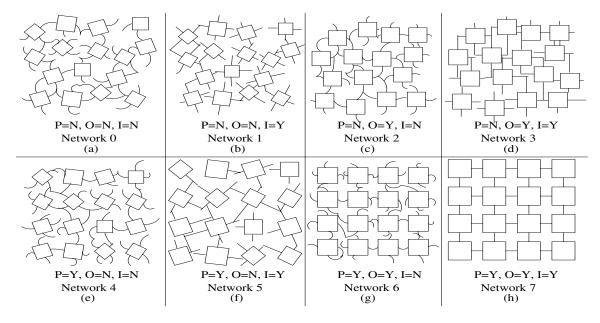

| Figure 8-2.  | Multiple Intersecting links                                       |

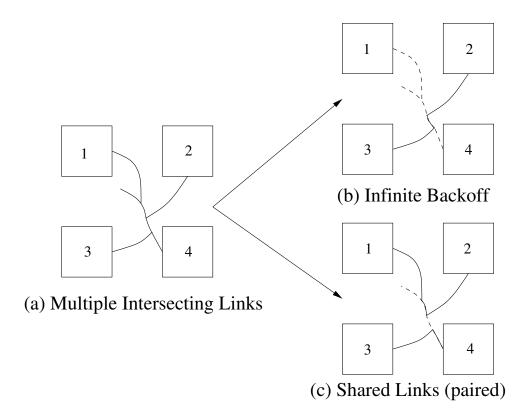

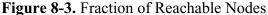

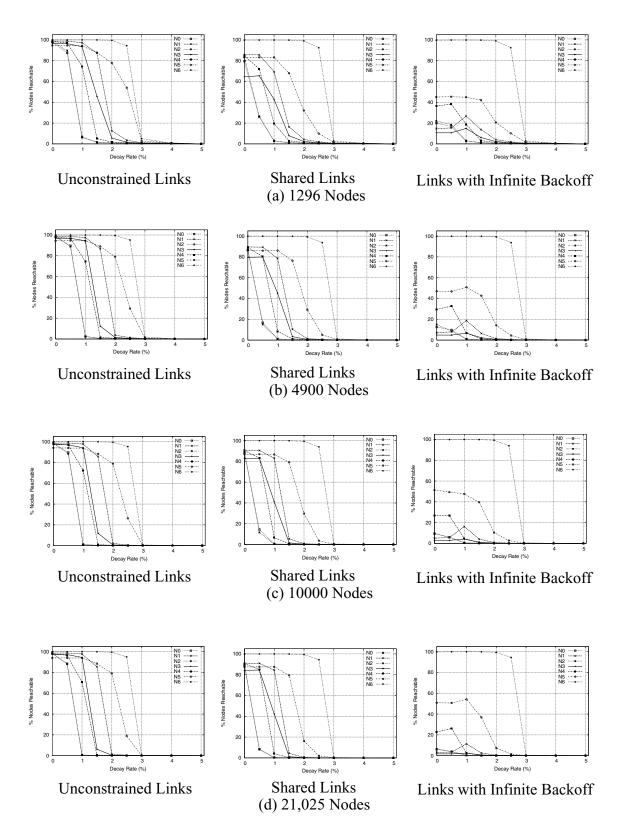

| Figure 8-3. | Fraction of Reachable Nodes                        | 147 |

|-------------|----------------------------------------------------|-----|

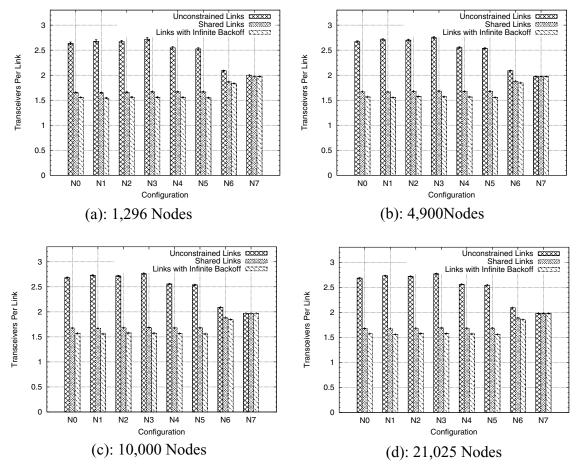

| Figure 8-4. | Transceivers Per Link                              | 148 |

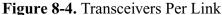

| Figure 8-5. | Average Active Links Per Node                      | 149 |

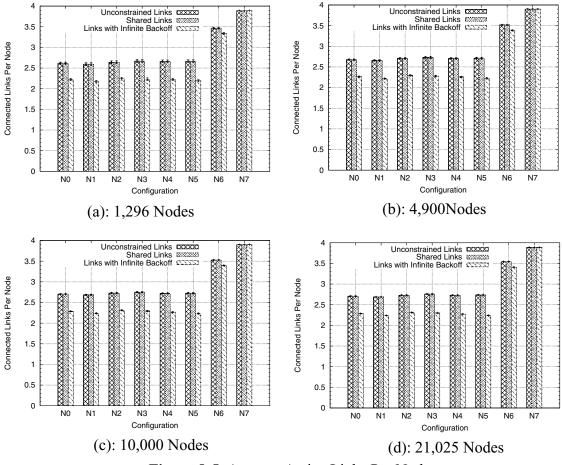

| Figure 8-6. | Sensitivity to Decaying Growth Rate                | 150 |

| Figure 8-7. | SOSA performance sensitivity to different networks |     |

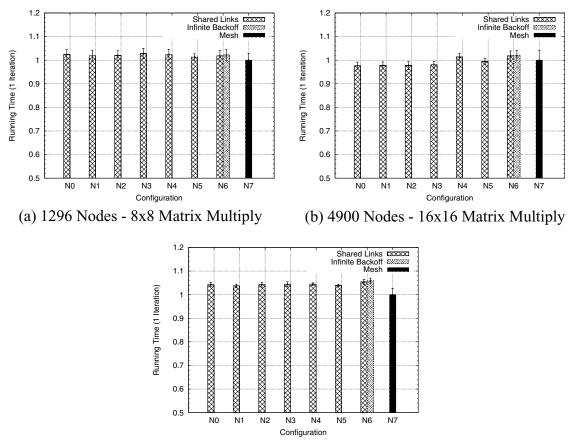

| Figure B-1. | Matrix Multiplication - N3 algorithm               |     |

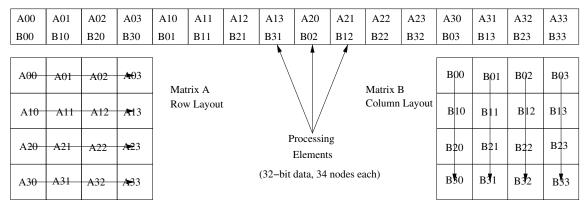

| Figure B-2. | Matrix Layout                                      |     |

| Figure B-3. | Matrix Multiply: Assembly Code - No Optimizations  | 184 |

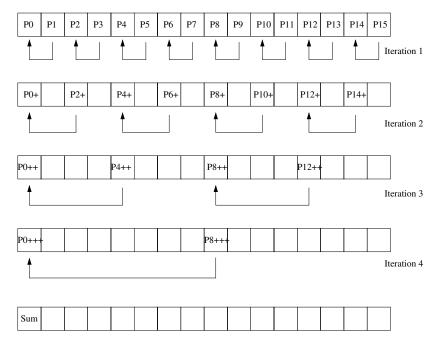

| Figure B-4. | Logarithmic Accumulate                             |     |

| Figure B-5. | Matrix Multiply: Assembly Code - No Optimizations  |     |

# 1 Introduction

The development and continued scaling of CMOS technology has enabled the tremendous growth of the computer and electronics industry over the past three decades. The semiconductor industry continues to meet and even exceed the pace dictated by Moore's law [95], which states that the number of transistors that can be packed on a chip doubles every 18 months. The decrease in device size has enabled a reduction in the size and power consumption of microprocessors, while providing designers with the flexibility to implement greater functionality to match the needs of a wide range of target applications. The increase in computational capabilities of microprocessors has also been matched by a corresponding increase in the computational demands of application software that runs on them. This has been complemented by the development of software applications that depend on the new features implemented in microprocessors, resulting in a positive feedback loop between hardware functionality and software requirements. The demand for increasing computational power in microprocessors is unlikely to diminish in the near future as we rely on computers to develop new drugs [30,118], understand and process genomes [146], predict the weather [32], study natural phenomena like earthquakes [79], create highly realistic virtual environments [25,96,132] and to design and test computers [154].

However, CMOS scaling is soon expected to reach physical limits that will make it difficult, if not impossible, to build smaller transistors with the required electronic properties [66,67,68]. Researchers have developed several new devices that could replace CMOS based transistors, including carbon nanotube transistors [10,138], silicon nanorod based transistors [26,63,93], single electron transistors [8] and even transistors made using organic molecules [22,24,141]. Preliminary studies have shown that these devices could be used in building circuits that can operate at higher speeds and consume lesser power, while being packed at higher densities than CMOS based devices. This would allow us to maintain Moore's law beyond CMOS.

Also, as CMOS technology is scaled into the nanometer range, some assumptions about circuit properties that were true for larger device sizes are invalidated. For example, until recently, it was safe to assume that dynamic (switching) power was the only significant source of power consumption and it was safe to neglect static or leakage power. It has also been safe to assume that the circuits will largely function reliably, without frequent faults or defects. The scaling of CMOS and the use of emerging technologies to build circuits could invalidate some of these assumptions. For example, leakage power is now a significant fraction of the power being dissipated in modern CMOS circuits and can no longer be neglected. As circuits get smaller, reliable operation is no longer guaranteed due to manufacturing defects or faults during operation. The invalidation of these fundamental assumptions necessitates a re-examination of the process of circuit and architecture design when using emerging technologies.

The challenge to scaling CMOS extends to the top-down manufacturing process of photolithography used to build CMOS integrated circuits (ICs). Photolithography uses a combination of light sensitive chemicals and special 'masks' that define circuit patterns, to etch the circuits on a silicon wafer. This process is extremely sensitive to impurities, and needs a clean environment to manufacture reliable devices. As the size of devices reduces, the sensitivity to impurities increases and the tolerance to variations in manufacturing steps reduces. This has led to rising manufacturing costs [3] and increasing difficulty in achieving a high level of device reliability [15].

The increasing cost of optical lithography has led to an increased interest in bottom-up manufacturing techniques like self-assembly, that require less control during manufacturing. DNA-based self-assembly [126], one specific type of self-assembly, uses the wellknown assembly properties of DNA to build a scaffold-like framework in which electronic devices can be assembled. The ability to control the placement of electronic devices at specific points on the DNA scaffold is a critical requirement for the development of DNAbased self-assembly as a viable manufacturing technique. Researchers have recently made significant progress in achieving this goal by demonstrating the placement of aperiodic patterns on a DNA lattice [37,116,123,104] and the DNA-based self-assembly of nanowire transistors [129]. DNA-based self-assembly has the potential to significantly reduce manufacturing costs and opens up possibilities of constructing large scale systems with more than  $10^{12}$  active elements. This scale is three orders of magnitude greater than the near term projections for CMOS and is made possible by the parallel nature of self-assembly.

In this thesis, we explore the effect of one emerging manufacturing and device technology on computer architecture. We assume the use of DNA-based self-assembly of carbon nanotube based devices as the underlying manufacturing technology. Despite this assumption, the design and analysis of the architectures presented in this thesis is applicable to other technologies with similar characteristics. The rest of this chapter is organized as follows. We start with the main statement and primary contributions of this thesis (Section 1.1). Next, we briefly describe the challenges faced due to the use of DNA-based self-assembly of carbon nanotube based devices (Section 1.2), and present a short description of a defect tolerance mechanism (Section 1.3). We then present brief descriptions of two architecture designs (Section 1.4). Next, we describe our analysis of the trade-off between node complexity and control over self-assembly to improve system connectivity (Section 1.5). We conclude this chapter with an outline of the structure of the thesis (Section 1.6).

#### **1.1 Thesis Statement and Contributions**

The main goal of this thesis is to establish the validity of the following hypothesis: "It is possible to design a high-performance defect-tolerant architecture that can match or even outperform existing architectures while operating at a lower speed, consuming less power and using at most the same area, despite the assumed limitations of DNA-based self-assembly of nanoelectronic components."

This thesis makes four primary contributions:

- We develop a circuit architecture for DNA-based self-assembly of nanoelectronic devices that requires system designers to balance the use of simple, regular building blocks to build complex circuits, while tolerating defects,

- 2. we adapt an existing mechanism to provide logical structure and tolerate defects in a random network of computing blocks,

- 3. we design and evaluate NANA, a proof-of-concept general purpose architecture built on top of a random network of heterogeneous self-assembled nodes, and

- 4. we use the insight gained from NANA to design and evaluate SOSA, a SIMD architecture built on a random network of identical self-assembled nodes. The power and area estimates for SOSA obtained through circuit design, combined with its performance evaluation through simulation help establish the validity of the primary hypothesis.

#### **1.2 Impact of DNA-based Self-Assembly of** Nanoelectronic Components on Architecture Design

DNA-based self-assembly of nanoelectronic devices is a promising technology that may be used in constructing circuits by placing aperiodic patterns on a DNA scaffold structure, and assembling electronic devices at certain locations on the scaffold [109]. However, the assumed capabilities of self-assembly impose certain constraints on the size and complexity of the circuits that can be self-assembled. This limitation in size is unlikely to change without significant yield improvements in building DNA scaffolds. Another limitation of self-assembly is the limited or lack of control over the placement and orientation of these self-assembled circuit blocks ("nodes"). However, one of the primary advantages of self-assembly is the ability to manufacture a large number of these computational blocks in parallel. However, a lack of control over this parallel self-assembly can result in a random network of computational blocks once they have been connected through a second self-assembly step.

To design a computer system using these random networks of self-assembled nodes, computer architects must:

- (i) understand the characteristics of the random networks,

- (ii) devise a technique to impose logical structure on the random network,

- (iii) implement a mechanism to achieve defect tolerance,

- (iv) design an architecture that can exploit the large number of nodes, including developing an instruction set and execution model and,

- (v) determine the functionality that must be implemented in the limited sized nodes.

At minimum, these nodes must have the ability to communicate with each other, perform some computation, and store some state. Step (v) is critical since the capabilities of the nodes determine the capability of any computer system built using them, and an efficient node design can help maximize this capability. This thesis explores each of these steps and presents the design and evaluation of two different architectures built on a random network of self-assembled nodes.

#### **1.3 Defect Tolerance**

As discussed in the previous section, defect tolerance is one of the primary requirements of any architecture built using emerging nanotechnologies. We design a mechanism for achieving defect tolerance by modifying an existing broadcast algorithm to isolate defective nodes and to impose a logical structure on the random network of nodes [110]. This allows us to connect all functional nodes that can be reached from the node where the broadcast is initiated. The defect tolerance mechanism requires very simple hardware in each node and is able to tolerate a large node defect rate (up to 30% defective nodes). Both the architectures developed in this thesis use this defect tolerance mechanism to isolate defective nodes as well as to impart logical structure on the random network of nodes. In the next section, we present a brief overview of both architectures.

#### **1.4 Architectures for Self-Assembled Nanoscale Devices**

The first architecture (Nanoscale Active Network Architecture [111] or "NANA") targets general purpose workloads and supports the traditional Von-Neumann programming model and a memory system. This proof-of-concept architecture divides a heterogeneous random network of nodes into smaller groups of nodes called "cells" and constructs logically disjoint execution and memory networks within the cells. The isolation of the two networks reduces the physical resources required in each node in the system. Once the two logical networks are constructed, execution packets consisting of instructions and data operands in a specific order are routed in the execution network searching for appropriate resources to perform the operations specified in the instructions. A thorough evaluation of NANA using simulation and modeling reveals that it is unable to achieve good performance because of two primary reasons: 1) low node utilization and 2) bottlenecks in the memory system. The evaluation of NANA provides insight into performance problems that arise due to the execution model and highlights the limitations of the node interconnection network. Thus, while NANA fails to prove the thesis statement, it provides valuable insight into possible strategies that will or will not work in building a high performance architecture. It also demonstrates that it is possible to build a functional architecture that can tolerate high node defect rates.

The second architecture (Self-Organizing SIMD Architecture [112] or "SOSA") aims to achieve high node utilization by targeting data parallel workloads and supports the data parallel programming model. The architecture divides a homogenous random network of nodes into "cells", but each cell is further divided into computational blocks called "processing elements" or PEs. All PEs execute the same instructions, but operate on different data and are connected in a logical ring. This simplifies the programmer's view of the set of PEs and allows simple communication between PEs. Since all PEs execute the same instruction, a large fraction of nodes are active at the same time, allowing SOSA to better exploit the large number of nodes available. We perform a thorough evaluation of SOSA using a detailed simulator and circuit models of the node. We use a variety of circuit design tools - off the shelf (VHDL, HSPICE), as well as custom layout tools developed specifi-

cally for the underlying technology [41] to build a circuit model of the node, and to estimate its size and power consumption. We demonstrate that SOSA can tolerate node defects with the RPF algorithm by implementing fail-stop behavior for critical logic blocks within each node [107]. By simulating the execution of various programs on SOSA, we demonstrate that SOSA supports the primary statement of this thesis by exceeding the performance of existing architectures while operating at a lower speed and consuming lesser power.

#### **1.5 Improving Network Connectivity**

The process of self-assembly can be modified to provide control over node placement, orientation and creation of inter-node links. This adds additional complexity to the manufacturing process, but can result in simpler and more structured networks. Alternatively, the communication logic within each node can be augmented to support more complex protocols over inter-node links, thus improving system connectivity. We explore the trade-off between control over self-assembly and the added complexity required within each node to achieve good system connectivity [108]. We find that control over node placement and orientation results in better connected networks. However, by allowing each node to treat an inter-node link as a shared medium (i.e., a bus), we can achieve nearly the same degree of connectivity in an unstructured network.

#### **1.6 Thesis Outline**

This thesis is organized as follows. Chapter 2 provides background on DNA-based selfassembly, as well as carbon nanotube and other emerging device technologies. Chapter 3 studies the impact of DNA-based self-assembly of nanoelectronic components on architectural design, and describes the self-assembled circuit architecture that is used in the rest of this thesis. Chapter 4 describes a mechanism for tolerating defects in a random network of self-assembled computing blocks. In Chapter 5, we present the design and evaluation of NANA, a general purpose architecture built using random networks of heterogeneous selfassembled nodes. We present the design and evaluation of SOSA, a SIMD architecture built using random networks of homogenous self-assembled nodes in Chapter 6. We describe a modular design for fail-stop SOSA nodes and explore how such nodes enable the system to tolerate increased device failure probabilities in Chapter 7. In Chapter 8, we explore the trade-off between control over self-assembly and node complexity to maximize network connectivity. Chapter 9 discusses other research related to this thesis and Chapter 10 concludes this thesis.

## 2 DNA-Based Self-Assembly of Nanoelectronic Devices

Photolithography has been the primary manufacturing technique used to build microprocessors and other integrated circuits for the last three decades. The semiconductor industry has been able to improve performance of circuits by reducing the size of devices manufactured. However, as CMOS devices shrink into nanometer scales, further scaling is difficult and is approaching hard physical limits. This has led to a search for alternative nano-scale technologies that might replace CMOS based devices. In this chapter, we provide background information about DNA-based self-assembly and some promising nanoelectronic devices that have the potential to replace CMOS as the dominant technology for manufacturing microprocessors in the future. There are several promising candidates, including carbon nanotube based devices, single electron transistors, silicon nanowire transistors and organic molecules. Each of these devices have their advantages and disadvantages and are the subject of much research to improve their properties and make them suitable for use with manufacturing technologies of the future.

Improvements in the top-down manufacturing process of photolithography have allowed CMOS devices to be scaled into the nanometer range. However, as device sizes shrink, the costs associated with photolithography have been increasing rapidly. DNAbased self-assembly is a bottom-up manufacturing technique that has the potential to replace photolithography. Self-assembly techniques have the advantage of requiring low control over the manufacturing process and potentially enable the parallel assembly of a large number of devices at once resulting in lower manufacturing costs. For any combination of device and manufacturing technologies that are picked to replace CMOS, it is critical that they be compatible with each other. This makes the combination of DNA-based self-assembly and carbon nanotube based devices promising, since researchers have already demonstrated the ability to link DNA and carbon nanotubes [36]. We break our discussion of the underlying technologies into four parts, starting by discussing the reasons why alternatives to CMOS technology are required in the coming decades (Section 2.1). Next, we describe DNA-based Self-Assembly (Section 2.2), and various nano-electronic devices that could be viable candidates to be used with DNA-based self-assembly (Section 2.3). Finally, we describe the use of DNA-based self-assembly and carbon nanotubes (Section 2.4) to build circuits.

#### 2.1 End of Silicon Based CMOS

Silicon based CMOS devices have provided a stable platform for manufacturing complex microprocessors for over two decades. This has been achieved through advances in lithography, solid-state physics, and chemistry that have enabled a steady scaling down of device sizes. The semiconductor industry continues to meet and even exceed the pace dictated by Moore's law [95], which states that the number of transistors that can be packed on a chip doubles every 18 months. However, CMOS is nearing a point where further scaling is difficult if not impossible because of physical limits to building smaller transistors [66,67,68]. CMOS scaling faces additional hurdles due to the top-down manufacturing process of photolithography used to build CMOS integrated circuits (ICs). Photolithography uses a series of special 'masks' that define the patterns of circuits at various levels on the silicon wafer. ICs are manufactured using a combination of light sensitive chemicals, specific frequencies of light, metal interconnect and the masks. This process requires a very clean environment (typically less than 100 impurity particles per cubic meter of air). As the size of devices reduces, the sensitivity to impurities increases and the tolerance to variations in manufacturing steps reduces. As we progress further down on the nanometer scale, it is very hard to maintain the precision required during lithography. At nanometer scales, there is also increased vulnerability to electron tunneling, stray inductances and capacitances, transient faults caused by radiation, and defects. Setting up a manufacturing utility for 300mm wafers using 90nm technology costs more than one billion dollars [3]. This price will increase rapidly as the precision required during manufacturing increases. In addition, each chip requires many masks during the manufacturing process. As we shrink

device sizes, the masks need to be manufactured with greater precision. These mask sets already cost over one million dollars each to manufacture [3] and as device size shrink, these costs will increase.

The combination of exponentially increasing costs, reduced reliability, decreasing tolerance to manufacturing variations, and the rapidly approaching physical limits of scaling have led researchers to identify technologies that could replace photolithography and CMOS in the future. In the next section, we describe one bottom-up manufacturing technology (DNA-based self-assembly) that has the potential to replace photolithography and reduce costs.

#### **2.2 DNA-based Self-Assembly**

Figure 2-1. DNA double helix

DNA-based self-assembly is a bottom-up manufacturing process that uses the well-known assembly properties of DNA to build a lattice-like scaffold. Deoxyribonucleic acid or DNA is the primary carrier of genetic information in biological organisms. DNA consists of a chemically linked chain of molecules known as nucleotides, each of which consists of a sugar, a phosphate and one of four 'bases': adenine (A), thymine (T), cytosine (C) and guanine (G). A single nucleotide chain is also known as single-stranded DNA or ssDNA and can be defined by the sequences of bases present along the chain. The most stable form of DNA is a pair of nucleotide chains that link to form the well

known double helix structure shown in Figure 2-1. The nucleotide chains pair through hydrogen bonding of the bases, where adenine pairs with thymine and cytosine pairs with guanine. While other base pairings are possible, they are not as stable as the A-T and C-G pairings.

Figure 2-2. DNA lattice with repeating cavities [105]

The precise binding rules of DNA make this a promising technique to use with nanoscale devices. By specifying a particular sequence of base pairs on a single strand of DNA, we can exploit the base-pair rules as organizational instructions [120,126]. A region of ssDNA and its complement can act as 'tags' (T and T') for orienting objects in 3-space. The sequence of bases on the ssDNA must be carefully designed to minimize the probability of 'partial matches' where some non-complementary bases are forced to match due to the structure of other proximal base pairs [39]. Such carefully designed DNA tags can be used to create 2D patterned nanostructures [149] by combining the right fractions of synthetic ssDNA tags and annealing them by heating beyond their melting point and cooling slowly. Although the resulting structure can be used to perform computation [6, 119], we are interested in DNA's ability to self-assemble into large-scale nanostructures. Of particular interest to this thesis, is a structure that creates a 'waffle'-like lattice with repeating cavities [81,151,152] (see Figure 2-2). This type of lattice has been experimentally demonstrated and can achieve sizes that extend beyond 3 microns on each side (i.e., > 150 cavities on a side). This scaffold can be used to place and interconnect devices by forming tags at specific lattice points [150] and using a technique for attaching the appropriate complementary ssDNA tags [36]. The DNA self-assembly technique is independent of the specific nanoelectronic device used, however the limited size of each lattice (node) presents challenges for creating large sophisticated circuitry. Before we describe methods for building circuits,

we discuss some promising emerging devices. We focus our discussion on one specific device technology that is used in the rest of this thesis.

#### 2.3 Emerging Nanoelectronic Devices

As the scaling of CMOS devices faces technological hurdles, researchers have been searching for new nano-scale devices that could potentially replace CMOS in the long term. There are a number of choices for building nanoelectronic devices and wires [10,26,63,93,138,141]. These include nanocells [141], silicon nano-rods [93], carbon nanotubes [10,138], and silicon nanowires [26,63], most of which have the potential for building transistors that are smaller than conventional CMOS transistors. Carbon nanotubes (CNTs) [64,87] are cylindrical molecules of carbon that resemble rolled sheets of graphite, and can be single-walled (SWNT) or multi-walled (MWNT). Single-walled nanotubes can be metallic or semiconducting depending on a property known as their 'chirality', which describes the atomic structure of the CNT.

One promising device is a field effect transistor constructed using carbon nanotubes (CNFET) [70,75,138] in which application of a gate voltage [49, 138, 148] modulates the conductivity of a semiconducting nanotube. Recent advances enable separating metallic nanotubes from semiconducting nanotubes, precisely controlling the length of individual nanotubes [89,135,155] and self-assembly of carbon nanotube based electronic devices [57]. Therefore, we could use both types of carbon nanotubes to construct logic gates, memory (e.g., with cross-coupled NOR gates), and circuit interconnect. The fact that CNFETs are amenable to self-assembly makes this an attractive alternative, or supplement, to silicon device technology. CNFETs are naturally p-type, but research has demonstrated the ability to electrostatically dope them to be n-type [10].

It is useful to compare the estimated latency of CMOS devices and CNFET based devices. We compare the delay of NAND gates in CMOS against CNFET NAND gates. The data for the CNFET NAND gates are based on empirical SPICE simulations [40,17, 94]. The CMOS data is obtained from the ITRS roadmap [14] and from standard industry processes [4,1,2]. The ITRS data represents target delays for specific CMOS technology

Figure 2-3. CMOS vs. CNFET

sizes and is not measured data from devices. In fact, there are no know solutions for manufacturing CMOS devices smaller than 65nm in bulk (Intel is currently developing a 45 nm technology, details of which are not publicly available). Figure 2-3 compares the estimated latency of CMOS NAND gates against the latency of CNFET based NAND gates. The solid line represents CMOS delay estimates that have demonstrated solutions. The dashed line represents 'desired' CMOS delay estimates that are part of the 'red brick wall' (no known solution exists). The dotted line at the bottom represents the CNFET delay. We can see that even with current CNFET based devices, the delay is lower than most CMOS technology nodes. This demonstrates the potential of CNFET devices to provide an alternative to CMOS based transistors in the future.

For CNFETs to replace CMOS based transistors, they must be able to achieve comparable or higher switching speeds. One important property that determines maximum switching speed in a particular technology is the charge carrier mobility. Silicon and germanium based semiconductors have mobilities that are less than 2000 cm<sup>2</sup>/V-s [88]. Recent work in measuring the mobility of charge carriers in carbon nanotubes [33] indicates that the mobility is likely to be over 100,000 cm<sup>2</sup>/V-s. Thus, the delay estimate obtained from the SPICE model is probably pessimistic. It is likely that CNFET based devices will operate at frequencies as high as 1 THz [18], and have already been tested at frequencies of over

**Figure 2-4.** A DNA scaffold for nano-electronic circuits with patterned letter A (from [104])

10 GHz [121]. Next, we describe how DNA-based self-assembly could be used to manufacture CNFET based devices and build circuits.

#### **2.4 DNA-based Self-Assembly of Carbon Nanotube Electronics**

Researchers have demonstrated the ability to connect DNA to carbon nanotubes [36], enabling an assembly process that allows the placement of carbon nanotube based electronic circuits on a DNA lattice. Other potential materials (e.g., nanorods, silicon nanowires) could be substituted for the carbon nanotubes without loss of generality. A key requirement of this self-assembly process is the ability to control the placement of the electronic devices at specific points on the DNA scaffold to form a circuit. Researchers have recently taken two significant steps towards this by demonstrating the placement of aperiodic patterns on a DNA lattice [104,116,123] and the DNA-based self-assembly of nanowire transistors [129]. Figure 2-4 shows an atomic force microscope image of a DNA lattice with the letter "A" patterned on it. This is a critical step towards building DNA scaffolded electronic circuits (nodes). Current limitations of the self-assembly process place restrictions on the size of the DNA lattice that can be constructed, which in turn limits circuit size. While the size of individual nodes is small, the parallel nature of self-assembly enables the construction of a large number (~10<sup>9</sup>-10<sup>12</sup>) of nodes. These characteristics impose significant implications on any circuit architecture that is built using this assembly process. In the

next chapter, we discuss the implications of DNA-based self-assembly of carbon nanotube electronic devices on circuit architecture and develop a nanoelectronic circuit architecture.

# **3** Implications for Architecture Design

The previous chapter provided background on DNA-based self-assembly, emerging nanoelectronic devices and how the two techniques could potentially be combined to build circuits. Before we build circuits, it is critical that we gain a thorough understanding of the capabilities and limitations of self-assembly due to its fundamentally different nature (as compared to photolithography). We expect that limitations of self-assembly in the near future will restrict our ability to place and route logic devices and interconnect on a DNA lattice, resulting in space overhead that is not typically found in CMOS based devices. For example, while modern CMOS processes rely on more than ten layers of metal interconnect, DNA-based self-assembly is likely to be restricted to two layers in the near future. Any circuit design methodology must account for the routing overheads imposed by the limited metal layers. In this chapter, we present the implications of DNA-based self-assembly of carbon nanotube devices on circuit and systems architecture and develop a nanoelectronic circuit architecture that could be used to build computational circuit blocks. The circuit architecture uses aperiodic patterns on a DNA lattice to place nanoelectronic devices. This enables the construction of small circuits (nodes) that can perform computation or communicate with other nodes. We can then interconnect these nodes using wires. We propose the use of metallized DNA links, grown between nodes to create an interconnection network.

We analyze the implications of this circuit architecture on the design of system archictures. While our analysis assumes the use of DNA-based self-assembly of carbon nanotube based devices, it is applicable to other technologies with high defect rates and a loss of precise control over parts of the fabrication process (e.g., process variability and defects in scaled-CMOS). By using small, replicated building blocks to create larger systems, scaledCMOS based designs can mitigate the effect of increasing defect rates and process variability. We make the following contributions in this chapter:

- We propose a method for building circuits by placing carbon-nanotube based electronic devices in the cavities of DNA-lattices based on an analysis of the implications of DNA-based self-assembly on circuit architectures, and

- We determine that the assumed characteristics of DNA-based self-assembly limit us building small computational nodes with ~10,000 transistors, which is significantly smaller than conventional CMOS designs. The design of each node must balance communication, computation and defect tolerance capabilities within technological limits.

The rest of this chapter is organized as follows. We start with the implications of using DNA-based self-assembly of carbon nanotube electronics on circuit architecture design (Section 3.1). We then describe the basic circuit building blocks assumed in the rest of the thesis (Section 3.2). Next, we describe the architectural implications of using these self-assembled circuit building blocks (Section 3.3) and follow that with a list of challenges that must be overcome in the design of an architecture using this technology (Section 3.4). We conclude the chapter with a summary of the key concepts presented (Section 3.5).

#### **3.1 Implications for Nanoelectronic Circuit Architecture**

To use DNA-based self-assembly of carbon nanotube electronics as the manufacturing and device technology, a nanoelectronic circuit architecture must strike a balance between 1) the *regularity* of DNA self-assembly patterning capabilities, 2) the *complexity* required for sophisticated system designs and 3) *tolerance* to the inevitable defects present in nanoscale systems. The remainder of this section elaborates on each of these issues, focusing on the fundamental differences between this nanoarchitecture and current CMOS based architectures.

#### 3.1.1 Regularity

While the design of CMOS based circuits can be simplified by the use of regularity (e.g., standard cell VLSI), regularity is not a fundamental requirement. However, only periodic arrays of identical unit cells have been demonstrated on a large scale using DNA self-assembly technology. DNA self-assembly has a potential limitation in that the probability of incorrect tag matches increases as the number of unique tags increases. For each type of connection, we need a unique pair of complementary ssDNA tags. With more types of connections and a fixed number of base-pairs per tag, the tags become more similar (i.e., differ in fewer base-pairs) and partial matches become more likely. For example, if a functionalized nanotube binds to a partially matched tag, then it is in the wrong position. This situation is analogous to the Hamming distance [54] between encodings of symbols; if we need to encode more symbols with the same number of bits, then the Hamming distance is smaller and the probability of an error is greater. Minimizing the number of tags reduces the chances of partial matches, which could cause positional defects, during annealing. Therefore, repetitive structures are desirable, and circuit and system designers should strive to use them as much as possible.

#### 3.1.2 Complexity

Design complexity is a function of the number of different component types and the placement of these components. Current CMOS based circuits can arbitrarily place hundreds of millions of devices (both nFET and pFET) and wires with precision on the order of  $0.10\mu m$ . This precision is achieved by using photolithography to specify exactly where each individual component belongs. With the combination of carbon nanotube devices and DNA self-assemblies, we are trying to develop circuits that can perform useful computation. The components required to build circuits can be limited to CNFETs (as active devices), nanotube wires and metal plating for connecting wires. However, with DNA self-assemblies, we cannot specify component placement at the micro-scale with nearly the same degree of accuracy as CMOS. Complexity must be introduced without requiring a large number of

Figure 3-1. Two input CMOS NAND gate, and equivalent graph

tags. This mirrors the desire to use regular structures that minimize the number of tags. However, regular structures typically limit complexity.

Thus, the utility of self-assembled DNA arrays depends on the amount of complexity that we can introduce at various abstraction levels without causing an intractable number of partial matches. Consider a graph generated from the netlist of a transistor-level design of a combinational circuit (Figure 3-1). The vertices are transistor terminals and the edges are wires connecting the device terminals. A two-input CMOS NAND gate has eight vertices, and most combinational circuits require multiple NAND gates. Clearly, the naive approach of assuming a unique tag for each vertex in the graph requires a large number of unique tags (even ignoring fan-out issues). This will cause too many partial matches that create bridging faults (shorts), rendering the circuit mostly useless.

#### 3.1.3 Defect Tolerance

A defect is a permanent physical fault introduced during fabrication. We consider two types of defects: functional and positional. A *functional defect* corresponds to a component that does not perform its specified function (e.g., a transistor that does not conduct when it should). A *positional defect* corresponds to a (functionally correct) component that is

placed incorrectly. Both CMOS and DNA self-assembled nanoelectronics can incur functional defects, but only self-assembly is likely to incur positional defects. Positional defects can be both defects of omission and commission. An omissive positional defect occurs when a component is not placed where it belongs. A commissive positional defect occurs when a component is placed where it does not belong (i.e., the partial match described above). Omissive defects behave similar to functional defects. Commissive defects are more dangerous, since they can behave like bridging faults. For example, a misplaced nanowire could cause a short between power and ground or it could change circuit functionality in unpredictable ways (e.g., by erroneously connecting the output of a gate to its input).

In CMOS based circuits, there is limited support for defect tolerance. Photolithographic placement of components is a mature technology that incurs few defects. However, in architectures with hundreds of millions of devices and wires, defects will still occur with some probability (i.e., yield is less than 100%). CMOS microchips are thus tested for defects. If a defect is uncovered and it cannot be tolerated, the chip is discarded. However, some limited number of defects can be tolerated. For example, a defect in a cache or memory cell can be tolerated by systems that provide redundant cells and allow for re-mapping. Tests on the self-assembled circuits must be simple to allow the testing of a very large number of components. Ideally, each circuit must include basic self-test circuitry that can be triggered by external inputs.

Functional defect rates for carbon nanotube devices and positional defect rates for DNA assembled nanoelectronics are currently unknown due to the relative immaturity of the technologies. Functional defect tolerance could be achieved with the same techniques used in CMOS, since the problem is not fundamentally different. Tolerance of commissive positional defects, however, is a new challenge. Because of the unknown positional defect rates, the assembly approach used in this thesis is to first strive to minimize positional defects by exploiting regularity in DNA self-assemblies. However, as complexity increases and regularity decreases, the probability of positional defects increases, thus more sophisticated circuitry will require more defect tolerance.

Figure 3-2. DNA Scaffold for Nanoelectronics

Any circuit architecture that uses DNA-based self-assembly of nanoelectronic devices as the manufacturing process must strike a balance between the three conflicting goals of regularity, complexity and defect tolerance, as described in this section. Next, we develop one such nanoelectronic circuit architecture that could be used to build the computing blocks assumed in the rest of the thesis.

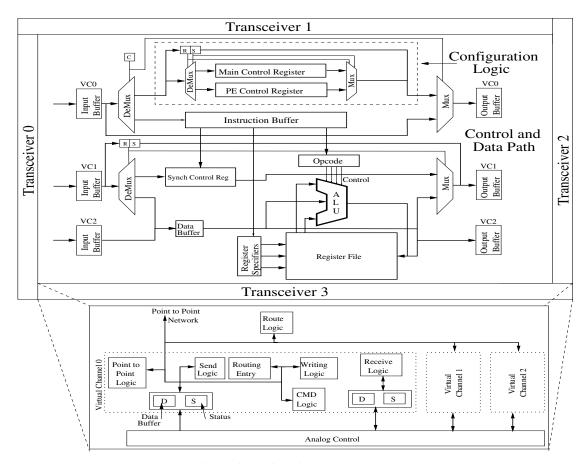

# **3.2 Nanoelectronic Circuit Building Blocks**

This section describes a nanoelectronic circuit architecture (shown in Figure 3-2) with structures based on a grid of CNFETs interconnected with conducting carbon nanotubes. At a high level, our proposed design addresses the conflicting goals of regularity and complexity by placing identical unit cells in the cavities of an aperiodic patterned DNA lattice. The lattice is regular in structure, but it has aperiodic binding points which can be used to connect the unit cells in complex patterns. This highlights a key difference between the proposed assembly process and existing approaches. Current nanoelectronic architectural approaches assume regularity in both the structure and the interconnect. We first present our initial proposed unit cell and then the proposed lattice. We then discuss how multiple building blocks could be self-assembled into a larger system. Finally, we describe how this system could interface with external circuitry.

#### 3.2.1 Exploiting Regularity: A Replicated Unit Cell

The proposed unit cell in our design is a three terminal CNFET sitting in the cavity of a DNA lattice. To place the CNFET in the cavity, we need to functionalize one semiconducting and one conducting nanotube such that they bind to the complementary ssDNA tags on the cavity edges and form a cross. We assume one of the nanotubes is wrapped in a thin insulating layer, such as  $SiO_2$  [48]. The conducting nanotube functions as the gate of the CNFET.

Using carbon nanotubes of a short length (~16nm) precludes commissive positional defects in which a carbon nanotube binds in two different cavities. By using two sets of tags in alternating cavities in each dimension (see Figure 3-2) and by using carbon nanotubes of a precise length, a nanotube cannot span across the DNA lattice to another cavity with the same tags. The distance between adjacent cavities is only 4nm, so if the same tag is used in adjacent cavities, then a nanotube may bind across the lattice arm rather than within a cavity. Using a checkerboard pattern of alternating tags with sufficient Hamming distance eliminates positional commissive defects. This approach requires carbon nanotubes of a precise length, which may be possible using a sonochemical method [87] to cut the originally long nanotubes into short segments and then using size-exclusion chromatography to separate the nanotubes by their length. This technique must be applied to both the semiconducting and conducting nanotubes.

We can augment this unit cell with short conducting carbon nanotubes that lie adjacent to the cavity on both the top and bottom of the DNA lattice. The short nanotubes are far enough apart to avoid cross-talk and may also be wrapped with an insulating polymer if necessary. The nanotubes initially would not intersect to form complete circuits. Instead, an electrical connection between nanotubes must be explicitly created by specifying an appropriate tag on the DNA lattice to which a gold nanosphere could bind. The nanosphere nucleates metal ions to form the connection with the help of an electroless plating process [16, 74]. Similarly, connecting transistors may require specifying whether the device connects to the top or bottom conducting nanotube. Forming these connections is where we add complexity to our design, and we explain how to introduce this non-regular patterning in Section 3.2.2.

The unit cell design fosters regular, repetitive structures. All nanotubes are the same length (16nm) and we require five sets of nanotubes that are functionalized with different tags. Four sets of nanotubes are used for the CNFETs; two semiconducting sets and two conducting sets. This corresponds to the two tag sets of the checkerboard pattern of cavity tags. A nanotube from one set can bind to any cavity with a complementary tag. Similarly, the interconnect nanotubes (the fifth set) can bind adjacent to any cavity directly on either the top or bottom of the DNA lattice in either the vertical or horizontal direction. This approach enables the use of a regular pattern for the base DNA lattice scaffolding.

# **3.2.2 Introducing Complexity: An Aperiodic Pattern for Interconnecting Unit Cells**

Our building block, while regular in structure, has aperiodic binding points for connecting together the nanowires of the unit cell. This aperiodic pattern could be achieved through either sequential assembly of tiles, extending recent work on one-dimensional aperiodicity [150] to two dimensions or through careful design of the DNA strands that comprise the unit cell to minimize assembly steps [104].

We could now potentially construct complex circuits by specifying the electroless plating points in the DNA lattice. For each of the top and bottom of the lattice, the plating point options include: the three transistor terminals to nanowire, interconnect nanowire in the vertical directions North and South, and interconnect nanowire in the horizontal directions East and West. We assume that to create a straight-through connection in the vertical direction requires both the North and South connections; similarly, both the East and West connections are required for a straight connection in the horizontal direction. We could build pass-throughs from the top-level interconnect to the bottom-level by connecting a transistor terminal to both interconnects.

Only a single tag on the DNA lattice is required to specify the plating points where the gold nanospheres can bind on the lattice. It is this tag that has the aperiodic pattern, and gold

will bind only where the tag appears. We note that this approach minimizes positional defects since the nanotubes are of specific lengths that can only bind in the appropriate positions of the lattice. In contrast, if we used long nanowires to connect distant points, then the number of tags to which they could potentially incorrectly bind is the number of tags on the circumference of a circle with radius equal to the nanowire's length.

#### 3.2.3 Large-scale Interconnection of Circuit Nodes